芯片烧录领导者昂科技术在发布新版本烧录软件的同时,同步宣布新增了多款兼容的芯片型号,其中包括奥拉半导体推出的去抖时钟芯片AU5615B00-QMR。目前,此芯片已经被昂科的通用烧录平台AP8000所支持。

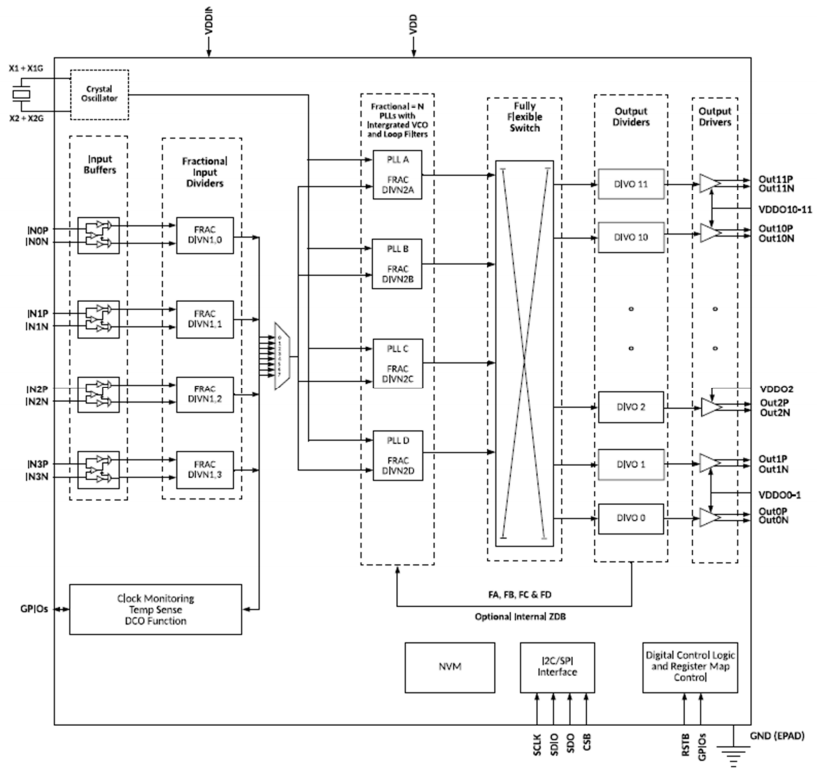

AU5615B00-QMR提供了可编程的四路基于小数频率转换的抖动衰减时钟合成器,提供灵活的输入到输出频率转换选项。超高的抖动性能DPLL可支持高达4个差分/8个单端的输入时钟,该输入时钟由4个小数频率转换器共用,并提供12个时钟输出。时钟输出以高度灵活的方式从4个PLL派生。

AU5615B00-QMR为9×9mm的QFN封装,采用了外部晶体。AU5615B00-QMR可以通过I2C/SPI接口来配置或者由工厂将客户所需的配置烧录在器件的非易失性存储器(NVM)中,NVM支持一次烧录。

AU5615B00-QMR

性能

• 超高性能PLL

• 全集成设计,无需外部元件

• 85fs典型RMS积分抖动(12k-20M)

• 70fs典型RMS积分抖动(采用嵌入晶体LGA封装)

• 122.88M输出,具有出色的近端相位噪声性能

• 完全灵活的输出和输入多路复用器:在PLL的输出分配中具有高度的灵活性

• 为数据转换器时钟提供JESD204B/C支持

• 外部EEPROM支持

• 频率控制DCO:所有输出端都提供DCO控制(0.001 ppt)

• 相位控制DCO:精细相位调节旋钮(调整精度<1ps),适用于闭环和开环模式下所有PLL输出端的相位

• 一流的无缝切换功能:PBO的相位跳跃低于25ps,PPG模式和Frequency Ramp模式可调频率/相位斜率

• 全集成的带宽可编程的环路滤波器,用于衰减抖动和漂移,低至0.09mHz

• 可重复的输入到输出延迟,具有输出相对延迟调整功能

• 内部ZDB模式的输入到输出延迟变化小于0.5ns(每个PLL都可独立启用此模式)

• 输出可在独立的同步脉冲上进行相位对齐

• 采用64引脚9×9mm的QFN/LGA封装

应用

• 电信级以太网

• OTN设备

• 微波回传

• 千兆以太网

• 无线基础设施

• 网络线卡

• 小基站

• 数据中心/存储

• SONET/SDH

• 测试/仪器仪表

• 广播视频

功能框图

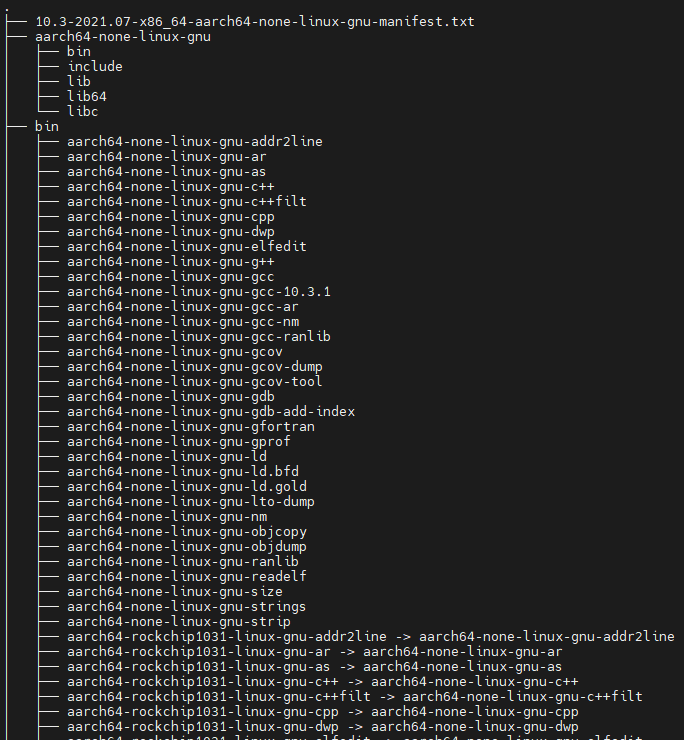

昂科技术自主研发的AP8000万用烧录器,已成为行业内具有标杆意义的专业烧录解决方案。该设备支持灵活可调的一拖一及一拖八配置模式,并提供在线、离线双工作模式,尤其针对eMMC、UFS等存储芯片开发了专属烧录方案,可全面覆盖奥拉半导体全系列芯片的裸片离线烧录与在板烧录需求。AP8000采用主机、底板、适配座三大核心模块的创新模块化设计,赋予设备出色的兼容性与扩展能力。作为通用型烧录平台,其不仅能适配市场上各类可编程芯片,更以稳定高效的性能表现,成为昂科自动化批量烧录设备IPS5800S的核心组件,可高效处理大规模芯片烧录任务,满足量产需求。

AP8000_通用烧录器_芯片烧录器

AP8000主机具备灵活的连接方式,同时配备USB和NET接口,可实现多台编程器的便捷组网。通过组网功能,用户能够轻松实现多台编程器的同步控制,高效开展并行烧录作业。在安全性方面,主机内置智能安全保护电路,可实时监测芯片放置状态与电路连接情况,一旦检测到芯片反插、短路等异常,将立即触发断电保护机制,全方位守护芯片和编程器的安全运行。主机内部搭载高速FPGA芯片,大幅提升数据传输与处理效率,确保烧录过程流畅高效。为增强使用便捷性,主机背部设置SD卡槽,用户只需将PC端生成的工程文件存储至SD卡,并插入卡槽,即可通过编程器实体按键完成文件选择、加载与烧录操作,实现脱离PC的独立运行。这一设计不仅降低了对计算机硬件配置的依赖,还简化了工作环境搭建流程,显著提升操作灵活性。

在扩展性与兼容性上,AP8000采用底板与适配板模块化组合设计,有效拓展主机功能边界。目前,该设备已实现对全主流半导体厂商产品的支持,覆盖PUYA, XILINX, ALTERA, GOWIN, LOGIC等知名品牌。其支持器件类型广泛,涵盖NAND, NOR, MCU, CPLD, FPGA, EMMC等,并全面兼容Intel Hex, Motorola S, Binary, POF等多种行业标准文件格式,为用户提供一站式、全场景的芯片烧录解决方案。

审核编辑 黄宇